# International Journal of Engineering Research and Generic Science (IJERGS) Available Online at www.ijergs.in

Volume - 4, Issue - 6, November - December - 2018, Page No. 99 - 104

## Design and Implementation of 8 Bit and 16 Bit ALU Using HDL Language

<sup>1</sup>Sudhanshu Vashistha, <sup>2</sup>Ragini Kumawat, <sup>3</sup>Tanvi Agarwal, <sup>4</sup>Yashwant Singh Sekhawat

<sup>1,2,3,4</sup> Department of Computer Science Engineering, Arya College of Engineering and Research Centre, Jaipur, India

Email: <sup>1</sup>Sudhanshu.vashistha85@gmail.com, <sup>2</sup>raginimirp@gmail.com, <sup>3</sup>ishuagar23@gmail.com

<sup>4</sup>rockstarstuntingysashwant@gmail.com

#### Abstract

The logical control element is a digital circuit that represents the central component of the computer processor. ALU is a diverse and very useful device that has many different calculations and logic such as multiplication, addition, logic or logic, logical XOR, etc. The optimized design of ALU is represented by Register Transfer Level (RTL) view. The ALU can be in different segments of bit such as 8-bit, 16-bit, and many more design process of CPU. In This paper deals with the designing of 8 bit and 16 bit ALU using HDL and Xilinx software.

Keywords: ALU, CPU, HDL, VHDL, RTL.

### Introduction

Algebraic logic (ALU) is a digital circuit that is used to perform arithmetic and logical operations. The inputs to the underlying operating unit are the data that is executed (called processes) and the selection line that refers to the process to be executed, where the result is the result of the completed operation. ALU will design the following operations:

- A. Arithmetical Operations

- B. Logical operations

In addition to the ALUs, the most recent CPUs contain a controller (CU). The ALU controller tells the process to perform with this The data and ALU store the result in the output register. The controller transfers data between recordings, ALU and memory. All the modules shown in the design are encoded using VHDL. The highest level module connects all stages to a higher level in the register transistor logic (RTL). RTL describes the data requirements and the controllers in terms of numerical logic to perform the desired operations. Each instruction in the Architecture Help Collection is defined in detail in RTL [1]. ALU performs basic and logical calculations.

Examples of calculations include addition, subtraction, multiplication and division. Examples of logical operations are comparisons of values such as NOT and AND & OR. All information on the computer is stored and manipulated as binary numbers, that is, 0 and 1 [2]. Transistor switches are used to process binary numbers because there are only two possible cases. Toggle: Open or Close. Represents the open transistor, which is not active, 0. The closed transistor, which is by the current one, is 1.

ALU is a logical circuit, which means that its output varies uniformly in response to input changes. In normal operation, fixed signals are requested for all ALU inputs and when enough time is received (or "propagation care call") for the signals propagated by the ALU it is the result of the operation of the ALU.

ALU is a logic circuit that can only get more inputs and outputs. The output of ALU only depends on the entries that are applied at that time and not on the previous conditions. The simple ALU consists of two inputs for the operation data, one for the selected operation and one for the result according to the specified operation.

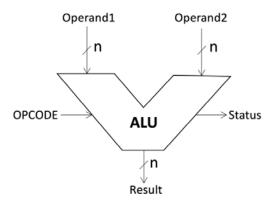

The symbolic symbol of the ALU and its input and output signals are indicated by arrows and refer to the ALU. Each action represents one or more signals. Enter the control signals to the left and take the outputs to the right; the data flows from top to bottom.

Figure 1: Basic ALU Design

## **Design of 8 Bit ALU:**

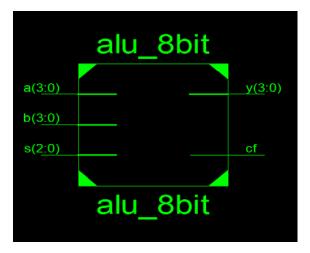

An 8-bit ALU unit can perform 8 different operations at the same time. It contains two 4-bit inputs for parameter data, a line of choice for 3-bit input, which determines the process to be performed on the data and the output of the result according to the specific process.

Table1: Basic Operation Of 8bit ALU Design

| S. no | Input value of S | Operatio<br>n |

|-------|------------------|---------------|

| 1     | 000              | A + B         |

| 2     | 001              | A -B          |

| 3     | 010              | A + 1         |

| 4     | 011              | A - 1         |

| 5     | 100              | A   B         |

| 6     | 101              | A & B         |

| 7     | 110              | A ^ B         |

| 8     | 111              | ~A            |

### RTL View of 8 bit ALU

Figure 2: Basic Block Diagram of 8-Bit ALU

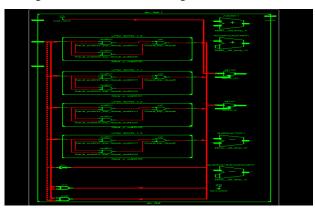

Figure 3: Logical Design of 8-Bit Proposed ALU

## **Simulation of 8 Bit Proposed ALU**

# Design of 16 -Bit ALU

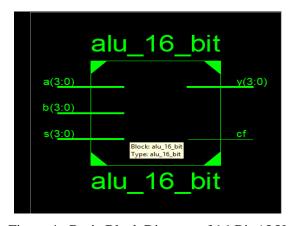

The 8-bit ALU has some drawbacks. It has fewer bits and is also limited to performing only 8 operations at a time. Therefore, the processing speed of an 8-bit ALU module is slower and more power consumption. To overcome these defects of the 8-bit ALU, we proposed a 16-bit ALU. The proposed 16-bit ALU consists of one arithmetic unit and logic

unit. A 16-bit ALU can perform 16 different operations at the time [3]. It contains two 4-bit inputs for parameter data, a line of choice for 4-bit input, which determines the process to be performed on the data and the output result according to the specified process. Here we will follow the principle "Divide and conquer" in order to use modules [4].

Table 2: Basic Operation of 16-Bit ALU

| S.no | Input value of S | Operation   |

|------|------------------|-------------|

| 1    | 0000             | A + B       |

| 2    | 0001             | A -B        |

| 3    | 0010             | A * B       |

| 4    | 0011             | B – A       |

| 5    | 0100             | A + 1       |

| 6    | 0101             | A-1         |

| 7    | 0110             | A + B + 1   |

| 8    | 0111             | A - B - 1   |

| 9    | 1000             | A   B       |

| 10   | 1001             | A & B       |

| 11   | 1010             | A ^ B       |

| 12   | 1011             | ~A          |

| 13   | 1100             | ~B          |

| 14   | 1101             | ~(A   B)    |

| 15   | 1110             | ~(A & B)    |

| 16   | 1111             | (A & B) + 1 |

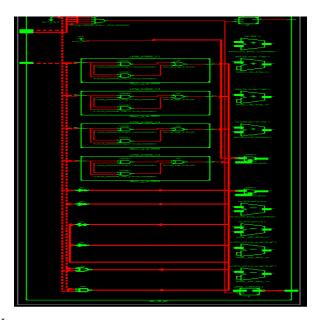

### **RTL View of 16-Bit ALU**

Figure 4: Basic Block Diagram of 16-Bit ALU

Figure 5: RTL View of 16bit ALU

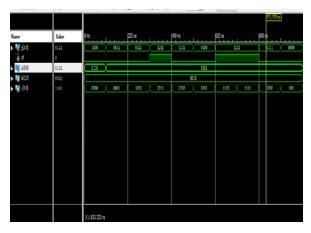

## **Simulation Of 16-Bit Proposed ALU**

### Conclusion

In this paper we propose design and implementation of 8-bit and 16-bit ALU with different 8 operations and 16 operations respectively. The main advantage of introducing 16-bit ALU design over 8-bit ALU is the achievement of increase in the operating speed of CPU so that the large number of different operations can be performed at a time. The RTL view shows the appropriate 8 and 16 bit ALU design and, finally, the simulation was performed to verify the general functionality of the ALU digital circuits through the formation of waveforms.

#### References

- Prachi Sharma, Rama Laxmi and Arun Kumar Mishra," Design of 16 bit Arithmetic and Logical unit using Vivado 14.7 and Implementation on Basys 3 FPGA Board", International Journal for Research in Applied Science & Engineering Technology (IJRASET), Volume 4 Issue VIII, pp-453-460, August 2016.

- 2. N. Ravindran and R. Mary Lourde, "AN OPTIMUM VLSI DESIGN OF A 16BIT ALU", International Conference on Information and Communication Technology Research (ICTRC2015),pp-52-55, 2015.

- 3. Chandni N. Naik, Vaishnavi M. Velvani, Pooja J. Patel, Khushbu G. Parekh, "VLSI Based 16 Bit ALU with Interfacing Circuit", International Journal of Innovative and Emerging Research in Engineering, Volume 2, Issue 3, pp-65-69, 2015.

- 4. Ankit Chouhan, Srishti dubey and Mr.Arvind Pratap Singh, "16-Bit Arithmetic And Logic Unit Design Using Mixed Type of Modeling In VHDL", International Journal of Engineering Research and Applications (IJERA) ISSN: 2248-9622, International Conference On Emerging Trends in Mechanical and Electrical Engineering ICETMEE), 13th-14th March 2014.